## High-Order Bandpass Sigma-Delta Modulators

#### $\mathbf{B}\mathbf{y}$

#### Stelian Mocanita

A thesis submitted to the

Faculty of Graduate Studies and Research

in partial fulfillment of the requirements

for the degree of Master of Engineering

Carleton University

Ottawa, Ontario

© Stelian Mocanita 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-36911-0

# The undersigned hereby recommended to the Faculty of Graduate Studies and Research acceptance of the thesis

#### "High-Order Bandpass Sigma-Delta Modulators"

#### submitted by

#### Stelian Mocanita

in partial fulfillment to the requirements for the degree of Master of Engineering

Chair, Department of Electronics

Thesis Supervisor

Carleton University

November 1998

#### **Abstract**

This thesis is part of the difficult taskwork to improve the effectiveness of the signal conversion between the complex analog world and the digital domain. A new switched-capacitor bandpass sigma-delta modulator structure, based on the sample-and-hold technique, that pushes the limits of speed in a given process, has been proposed. A new and fast switched-capacitor sample-and-hold resonator circuit has been presented. The  $\Sigma\Delta$  modulator design is decomposed into Z-domain noise and signal transfer functions and further into building blocks of amplifiers/resonators, etc.

The sample-and-hold circuits with 'voltage driven at both ends' capacitors are used. While existing clock feedthrough cancellation techniques are not beneficial here, switch turn-off transient simulations and a detailed analysis for different switch topologies are presented. A new study of the charge injection dependence on clock turn-off slope and time delay demonstrates the dummy switch technique as the best solution.

### Acknowledgments

I wish to acknowledge my profound appreciation to my supervisor, Martin Snelgrove, for his continuous support and guidance throughout the period of my master program.

I would like to thank Miles Copeland, Robert Harrison, Tad Kwasniewski and David Falconer for the knowledge I have acquired from the courses they taught at university. I also thank the university colleagues that supported me in my work.

I would like to also thank the National Sciences and Engineering Research Council of Canada and Mitel Corporation for their financial and technical support.

Special thanks to Rockwell Semiconductor Systems, San Diego design center, for their supportive attitude.

Finally, I wish to express my thanks and appreciation to my mother and all my family for their love and encouragement.

## **Table of Contents**

|           | Abstract iii                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Acknowledgments iv                                                                                             |

|           | List of Tables viii                                                                                            |

|           | List of Figures ix                                                                                             |

|           | List of Abbreviations and Symbols xiii                                                                         |

| Chapter 1 | Introduction 1                                                                                                 |

|           | 1.1 High-Order $\Sigma\Delta$ modulators 2                                                                     |

|           | 1.2 Clock Techniques 4                                                                                         |

|           | 1.3 Thesis Outline 5                                                                                           |

| Chapter 2 | The State of the Art 8                                                                                         |

|           | 2.1 BPΣΔ, High-Order, (1.5μm CMOS) 8                                                                           |

|           | 2.1.1 Topologies 9                                                                                             |

|           | 2.1.2 Cascade of Resonators with Feedforward Summation 10                                                      |

|           | 2.1.3 Cascade of Resonators with Feedforward Summation and Local Resonator Feedback Coefficient [Welland89] 11 |

|           | 2.1.4 Cascade of Resonators with Distributed<br>Feedforward, Feedback and Local Resonator<br>Coefficients 13   |

|           | 2.2 Delay Cells for $\Sigma\Delta$ 14                                                                          |

|           | 2.2.1 Half Delay Cell 14                                                                                       |

|           | 2.2.2 Full Delay Cell 16                                                                                       |

|           | 2.3 Double-Sampling S/H 18                                                                                     |

|           | 2.5 Conclusions 22                                                        |

|-----------|---------------------------------------------------------------------------|

| Chapter 3 | The ΣΔ Design 23                                                          |

|           | 3.1 SNR vs OSR 24                                                         |

|           | 3.2 NTF, STF Design 25                                                    |

|           | 3.2.1 Lowpass to Bandpass Transformation 27                               |

|           | 3.3 Cascade of SC Resonators Structure 28                                 |

|           | 3.3.1 NTF, STF equations 30                                               |

|           | 3.2.2 Stability by root locus 31                                          |

|           | 3.2.3 Simulation Results 33                                               |

|           | 3.4 Conclusions 37                                                        |

| Chapter 4 | The $\Sigma\Delta$ Circuit Implementation 38                              |

|           | 4.1 Fully Differential SC Resonator 39                                    |

|           | 4.1.1 Existing SC BP $\Sigma\Delta$ modulator circuits 39                 |

|           | 4.1.2 Four-path Resonator 41                                              |

|           | 4.2 Op-amps 48                                                            |

|           | 4.2.1 Choices Comparison: telescopic, folded-cascode two-stage op-amps 48 |

|           | 4.2.2 The Differential Folded-Cascode Op-amp 50                           |

|           | 4.2.3 CMFB 53                                                             |

|           | 4.2.4 Biasing Scheme 54                                                   |

|           | 4.3 Tri-level Quantizer 55                                                |

|           | 4.3.1 Tri-Level Flash ADC 56                                              |

|           | 4.3.2 Comparators 57                                                      |

2.4 Switches and Charge Injection 19

|            | 4.5 Conclusions 59                                          |

|------------|-------------------------------------------------------------|

| Chapter 5  | Switches and Clock Generator 61                             |

|            | 5.1 Switches Configuration for Charge Injection Analysis 63 |

|            | 5.2 The Switch Analysis 69                                  |

|            | 5.3 The Effect of Turn off Slope 80                         |

|            | 5.4 The Effect of Time Delay 82                             |

|            | 5.5 Proposed Switch 85                                      |

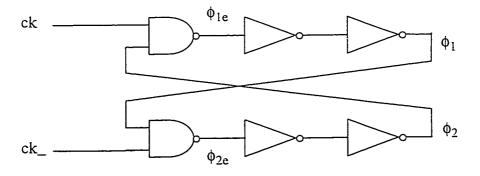

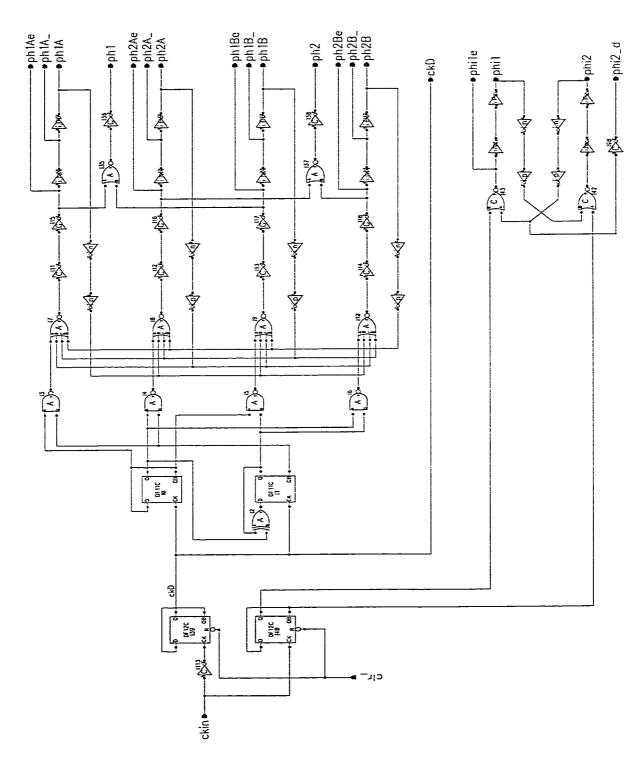

|            | 5.6 The Clock Generator 86                                  |

|            | 5.6.1 Non-Overlapping Clock 87                              |

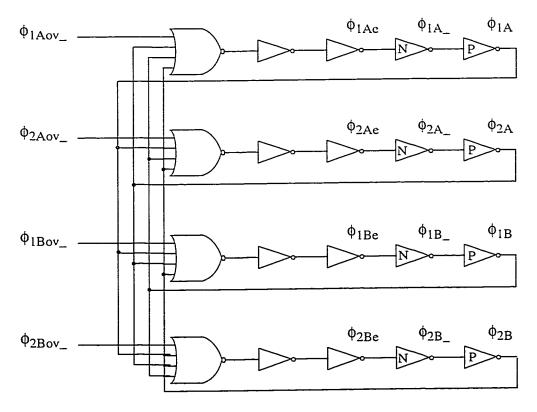

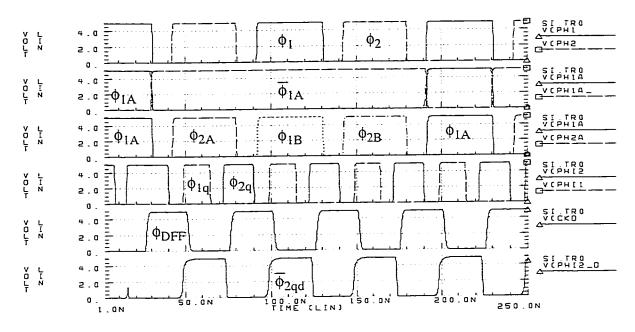

|            | 5.6.2 Four-Phase Non-Overlapping 88                         |

|            | 5.6.3 The Clock Drivers 89                                  |

|            | 5.7 Conclusions 90                                          |

| Chapter 6  | Summary and Conclusions 92                                  |

|            | 6.1 Summary 92                                              |

|            | 6.2 Final Conclusions 95                                    |

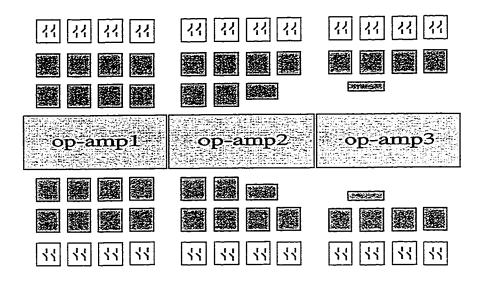

| Appendix A | Layout Considerations 97                                    |

|            | A.1 Mixed-Signal Paths 97                                   |

|            | A.2 Power supplies 99                                       |

|            | A.3 Element matching 99                                     |

|            | A.4 Floorplanning 101                                       |

|            | A.5 Conclusions 103                                         |

|            | References 104                                              |

|            |                                                             |

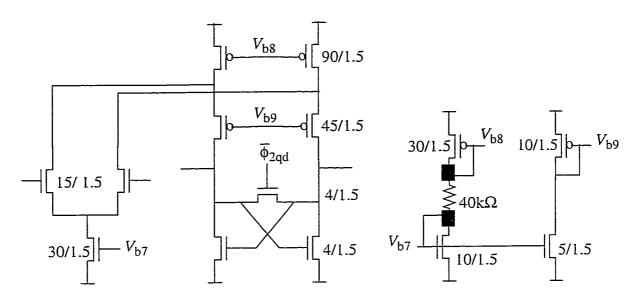

4.4 The D/A 58

## **List of Tables**

| Table 3.1 | Complexity vs performance of other art. 24                |    |

|-----------|-----------------------------------------------------------|----|

| Table 5.1 | Models and formulae used for charge injection prediction. | 73 |

| Table 5.2 | Charge splitting coefficients from [Vittoz85]. 74         |    |

# **List of Figures**

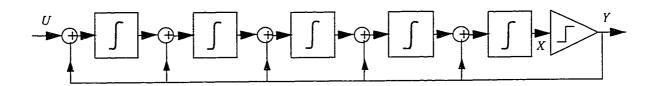

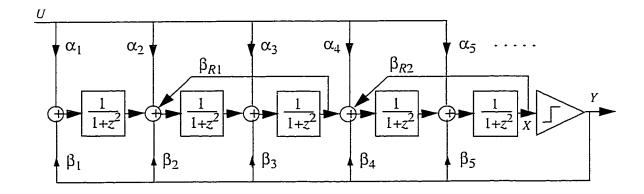

| Figure 1.1  | Single-loop high-order $\Sigma\Delta$ modulator structure. 3                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

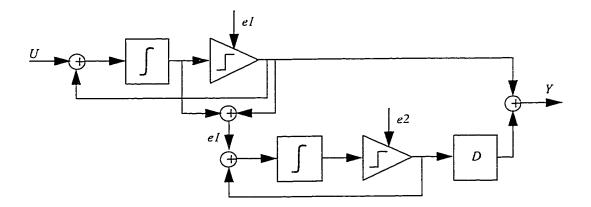

| Figure 1.2  | MASH $\Sigma\Delta$ modulator structure. 4                                                                                                           |

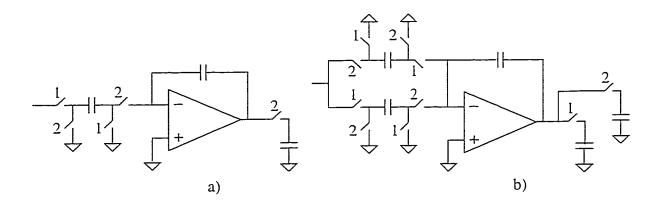

| Figure 1.3  | Typical a) single-sampled integrator, b) double-sampled integrator. 5                                                                                |

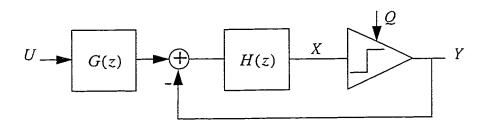

| Figure 2.1  | Structure of $\Sigma\Delta$ modulator (linear model). 9                                                                                              |

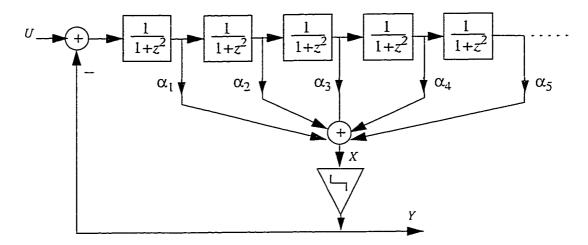

| Figure 2.2  | Cascade of resonators with feedforward coefficients. 11                                                                                              |

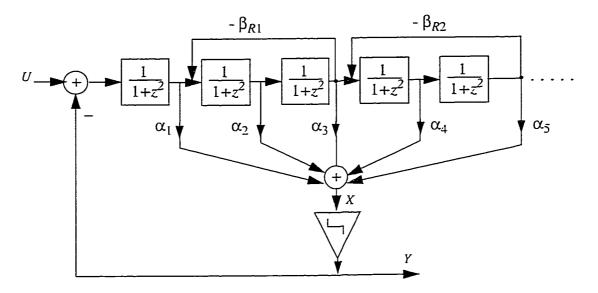

| Figure 2.3  | Cascade of resonators with feedforward summation and local resonator feedback coefficient. 12                                                        |

| Figure 2.4  | Cascade of resonators. 12                                                                                                                            |

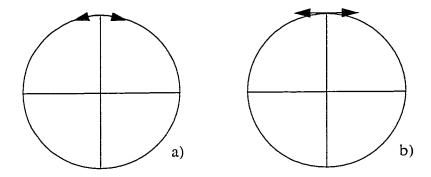

| Figure 2.5  | The NTF zeros split a) along the unit circle, b) along the tangent to the unit circle. 13                                                            |

| Figure 2.6  | Cascade of resonators with distributed feedforward, feedback and local resonator coefficients. 14                                                    |

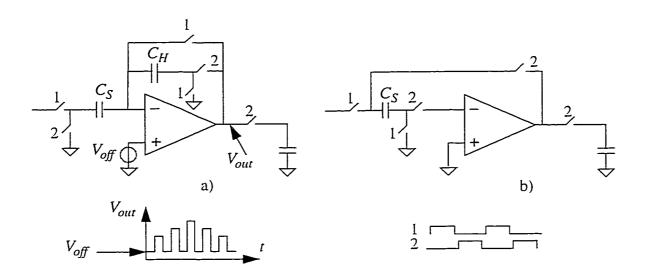

| Figure 2.7  | SC half-delay circuits: a) offset cancelled, b) capacitor mismatch insensitive. 15                                                                   |

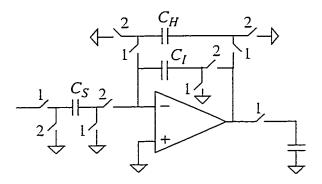

| Figure 2.8  | A full-delay sample and hold. 17                                                                                                                     |

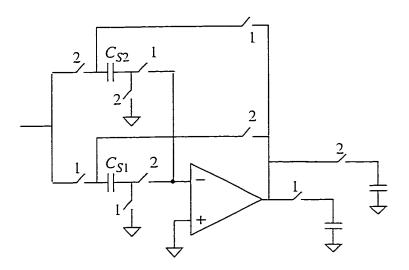

| Figure 2.9  | A full-delay double-sampling S/H (sample and hold). 18                                                                                               |

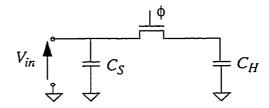

| Figure 2.10 | One-switch sample and hold circuit. 19                                                                                                               |

| Figure 2.11 | Vittoz curves. 20                                                                                                                                    |

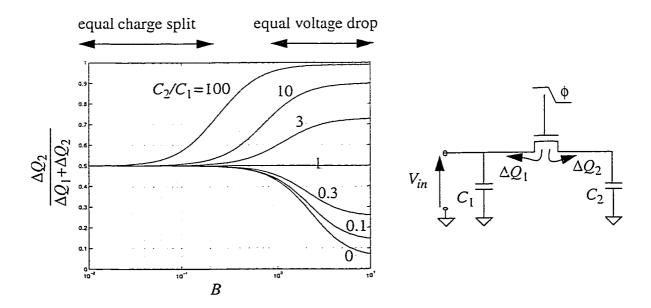

| Figure 3.1  | SNR versus oversampling ratio of a $4^{th}$ , $6^{th}$ , and $8^{th}$ -order $\Sigma\Delta$ modulator with a 2, respectively tri-level quantizer. 25 |

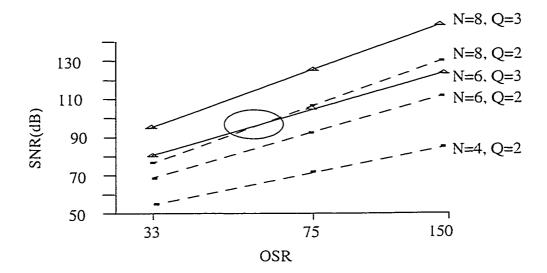

| Figure 3.2  | SNR vs $NTF$ 's out-of-band gain for a $6^{th}$ -order tri-level quantizer $\Sigma\Delta$ modulator(OSR=50). 26                                      |

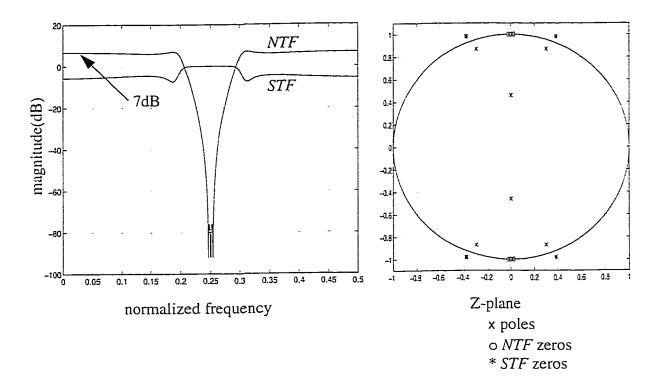

| Figure 3.3  | The magnitude of the $6^{th}$ -order <i>NTF</i> and <i>STF</i> , obtained from filtorX, with their poles and zeros. 28                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.4  | Block diagram of the $6^{th}$ -order bandpass $\Sigma\Delta$ modulator. 29                                                                                                                            |

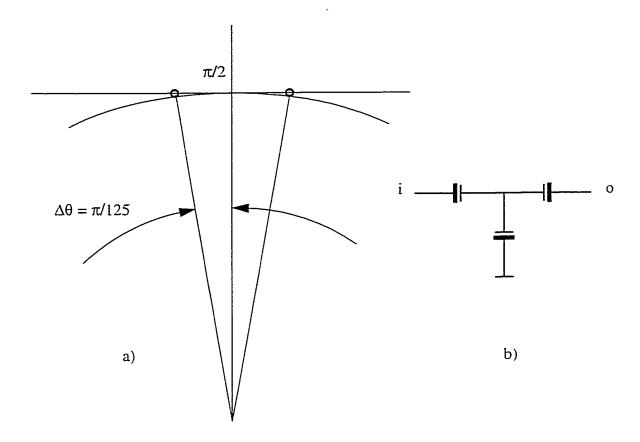

| Figure 3.5  | a) The NTF zero locations around $\pi/2$ ; b) implementation of the capacitor corresponding to $\beta = -0.0025$ 31                                                                                   |

| Figure 3.6  | Single loop $\Sigma\Delta$ modulator with the quantizer modelled as variable gain. 32                                                                                                                 |

| Figure 3.7  | Root locus of the third order lowpass $\Sigma\Delta$ modulator. 33                                                                                                                                    |

| Figure 3.8  | 131k points whole and inband spectra with input tone near $f_s/4$ . 34                                                                                                                                |

| Figure 3.9  | SNR vs input signal level for a bandwidth of 200kHz if clocked at 20MHz. 35                                                                                                                           |

| Figure 3.10 | Tonal behaviour for an input of -60dB relative to DAC levels (NTF's zeros are on the unit circle for the left-hand side inband spectrum, and outside the unit circle for the right-hand side one). 36 |

| Figure 3.11 | Whole and inband spectrum for 1% mismatch coefficients. 36                                                                                                                                            |

| Figure 4.1  | Op-amps of LDI and FE structures of [Singor94]. 39                                                                                                                                                    |

| Figure 4.2  | Pseudo-two-path resonator. 40                                                                                                                                                                         |

| Figure 4.3  | Clock waveforms for: quantizer $(\phi_{1q})$ , op-amp CMFB $(\phi_1)$ , resonator $(\phi_{1A}, \phi_{2A}, \phi_{1B}, \phi_{2B})$ . 42                                                                 |

| Figure 4.4  | Four-path two-delay resonator. 44                                                                                                                                                                     |

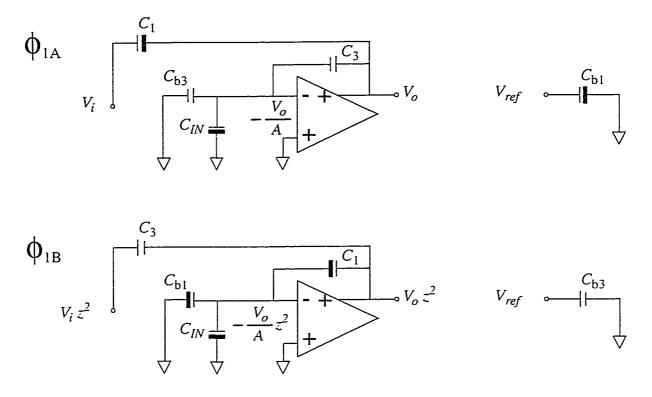

| Figure 4.5  | Resonator's circuits on $\phi_{1A}$ (top) and on $\phi_{1B}$ (bottom). 46                                                                                                                             |

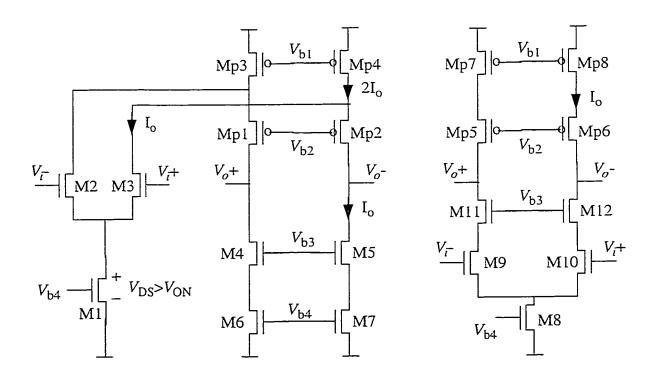

| Figure 4.6  | Folded cascode (left) and telescopic (right) op-amp schematics. 49                                                                                                                                    |

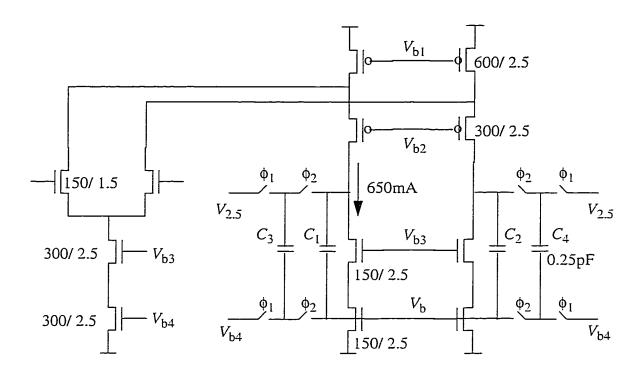

| Figure 4.7  | The differential folded cascode op-amp and its SC common mode feedback. 51                                                                                                                            |

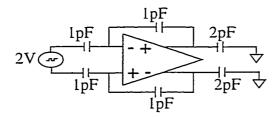

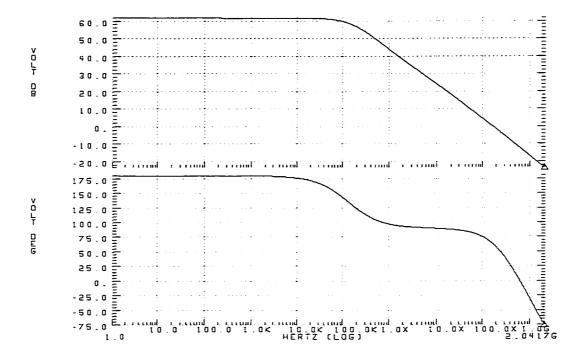

| Figure 4.8  | Op-amp test circuit for settling time. 52                                                                                                                                                             |

| Figure 4.9  | The folded cascode op-amp gain and phase for a 2pF load. 52                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

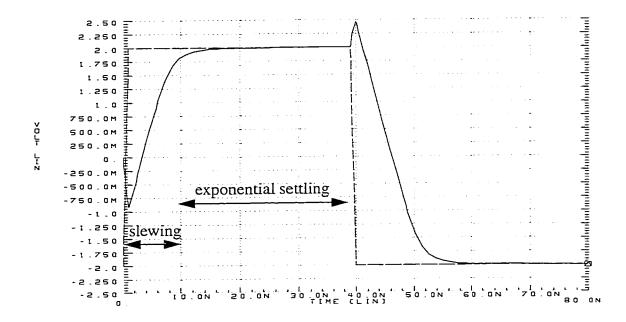

| Figure 4.10 | HSPICE simulation for the settling time. 53                                                                                                                                                                                                                                                                                   |

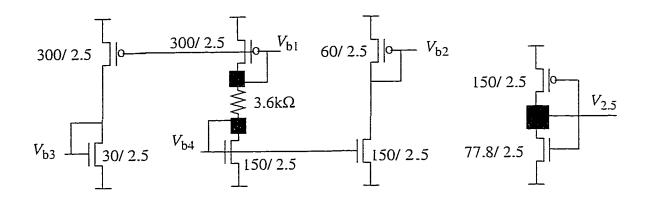

| Figure 4.11 | Op-amp bias circuits. 55                                                                                                                                                                                                                                                                                                      |

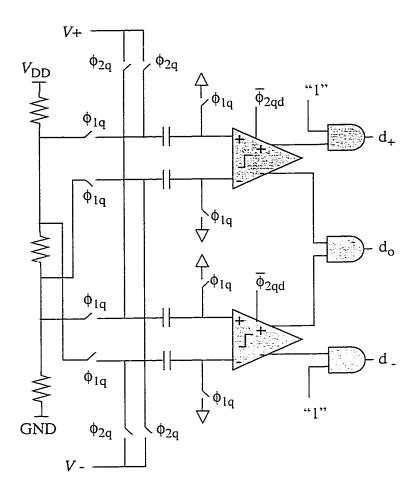

| Figure 4.12 | Tri-level flash ADC schematic. 57                                                                                                                                                                                                                                                                                             |

| Figure 4.13 | Comparator and its bias schematics. 58                                                                                                                                                                                                                                                                                        |

| Figure 4.14 | Tri-level differential D/A. 59                                                                                                                                                                                                                                                                                                |

| Figure 5.1  | The overlapping capacitance of an NMOS switch. 61                                                                                                                                                                                                                                                                             |

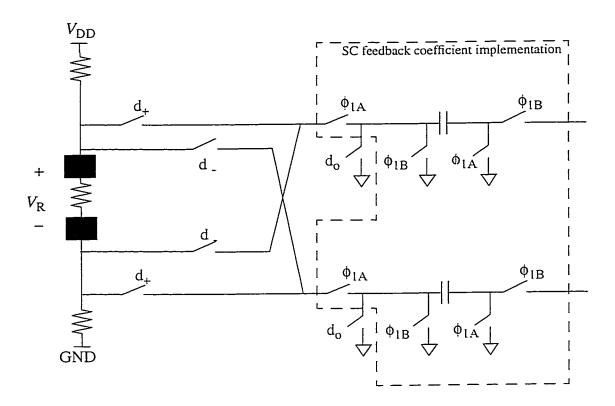

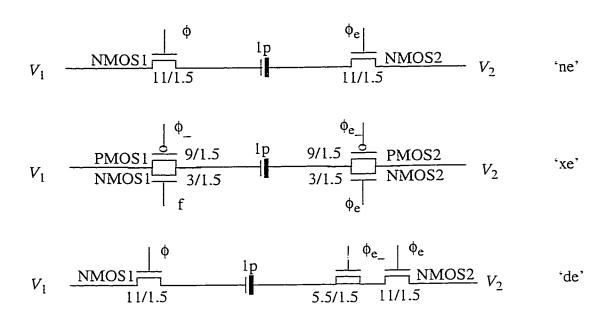

| Figure 5.2  | Simplified circuits for analysis of switches charge injection for NMOS (top), X-gate (middle), and NMOS with dummy (bottom) switches. The suffix 'e' denotes that an early version of clock is used. The 'bold' capacitor bottom plate has a parasitic capacitance of 100fF and a top plate parasitic capacitance of 10fF. 64 |

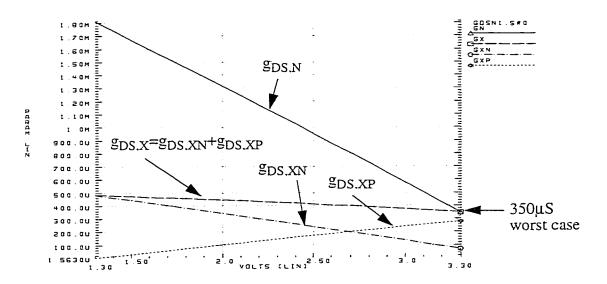

| Figure 5.3  | g <sub>DS</sub> vs voltage(1.3V to 3.3V) for NMOS and X-gate of Figure 5.2. 65                                                                                                                                                                                                                                                |

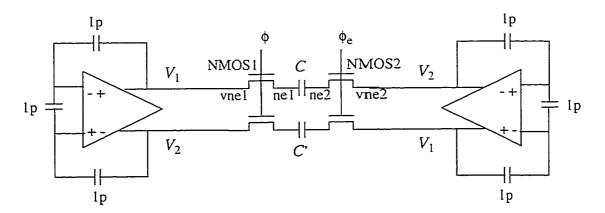

| Figure 5.4  | Fully differential test circuit for the NMOS switches charge injection. 66                                                                                                                                                                                                                                                    |

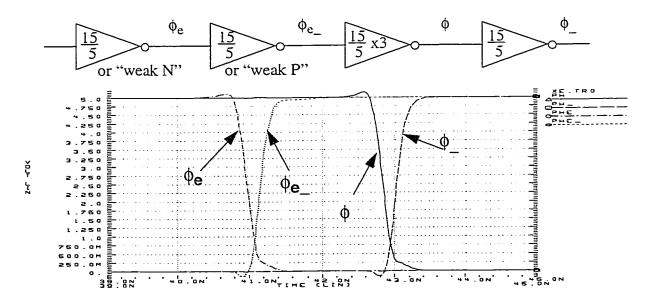

| Figure 5.5  | Clock circuit and waveforms for "higher slope" clock phases. 67                                                                                                                                                                                                                                                               |

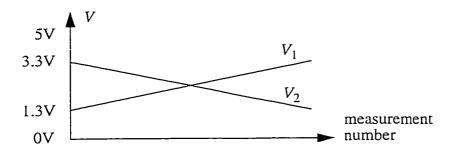

| Figure 5.6  | The voltages $V_1$ and $V_2$ that charge the capacitor. 68                                                                                                                                                                                                                                                                    |

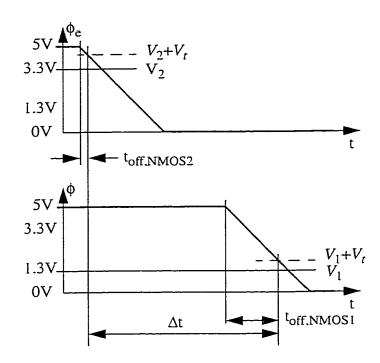

| Figure 5.7  | The clock phases for the NMOS switches defining the off-times. 70                                                                                                                                                                                                                                                             |

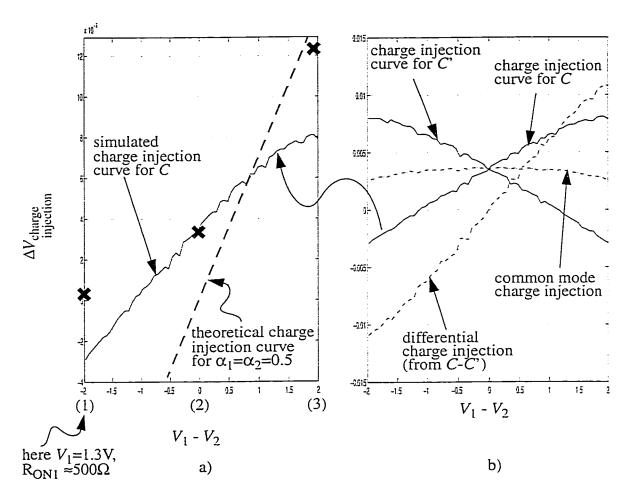

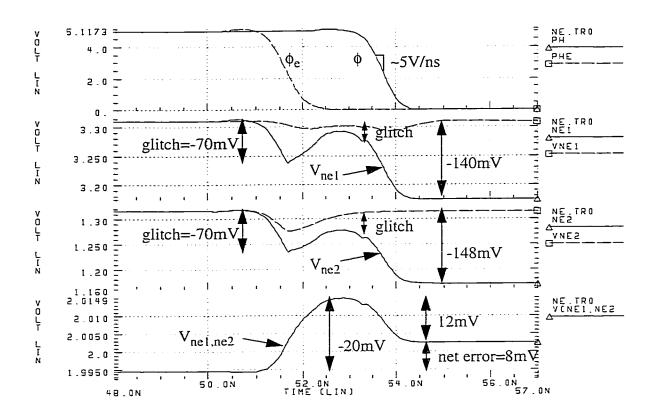

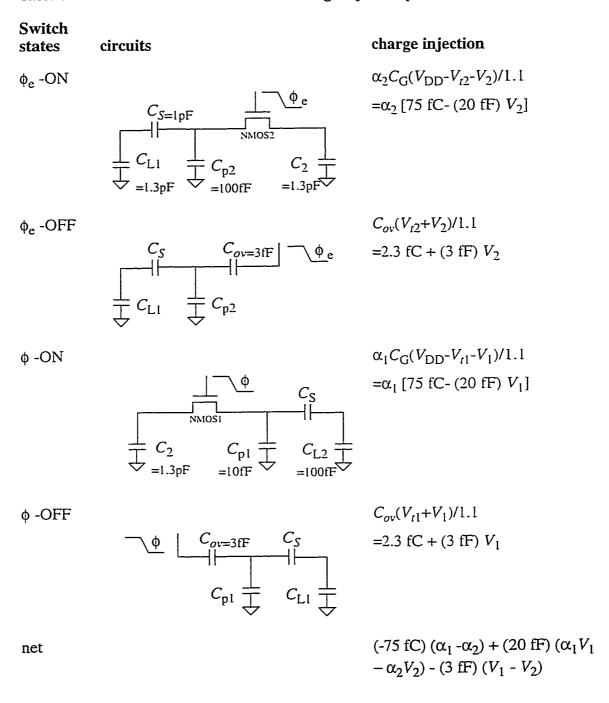

| Figure 5.8  | The charge injection voltage due to NMOS switches. The points marked 'x' are theoretical estimates based on the charge-sharing model of Vittoz. 71                                                                                                                                                                            |

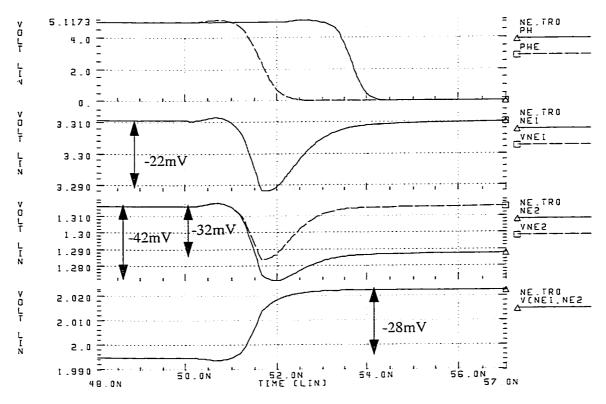

| Figure 5.9  | HSPICE waveforms for case (3) where $V_1$ =3.3V and $V_2$ =1.3V (clock is the top curve). This case was shown because the glitches are the most noticeable. 72                                                                                                                                                                |

| Figure 5.10 | Realistic model for the side impedances. The "II" to "L" transformation of [Romanowitz71] makes equivalent the left-hand-side circuits of NMOS2 as shown by the arrow. 75                                                                                                                                                     |

| Figure 5.11 | HSPICE waveforms when NMOS1 is replaced by a short-circuit. 76                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

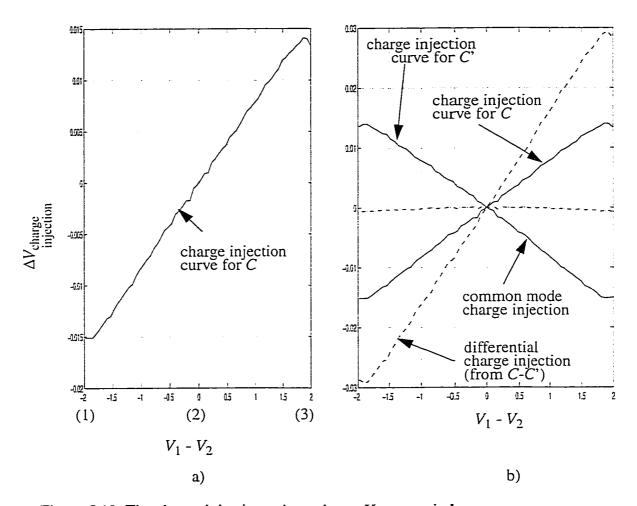

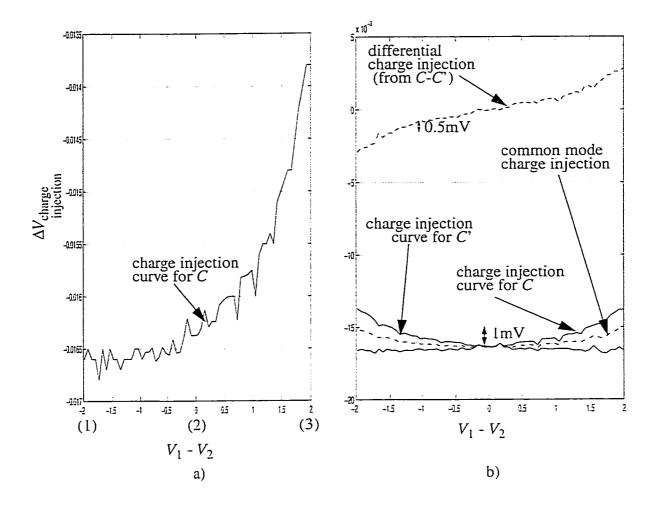

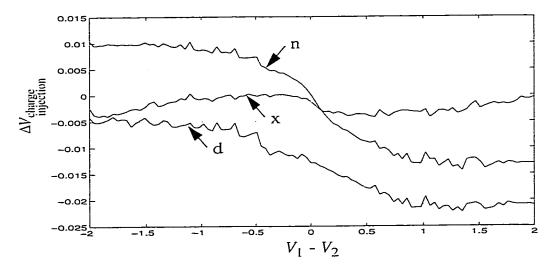

| Figure 5.12 | The charge injection voltage due to X-gate switches. 77                                                                                                                                                                                     |

| Figure 5.13 | The charge injection voltage due to dummy switch compensation. 79                                                                                                                                                                           |

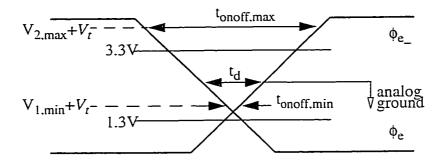

| Figure 5.14 | The qualitative clock phases for the NMOS switch with dummy. For $t_{onoff,max}$ the dummy compensates most of the NMOS2 charge. For $t_{onoff,min}$ the dummy compensates and adds extra to the charge from NMOS2. 80                      |

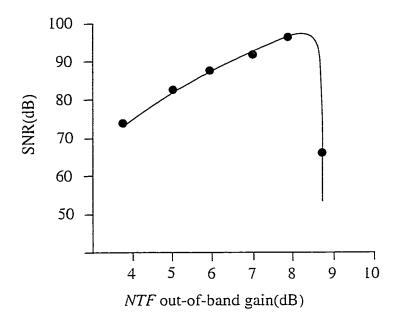

| Figure 5.15 | Charge injection chart according to [Vittoz85] and the corresponding circuit. 81                                                                                                                                                            |

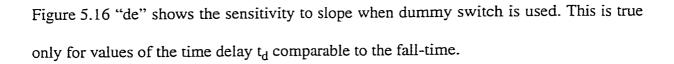

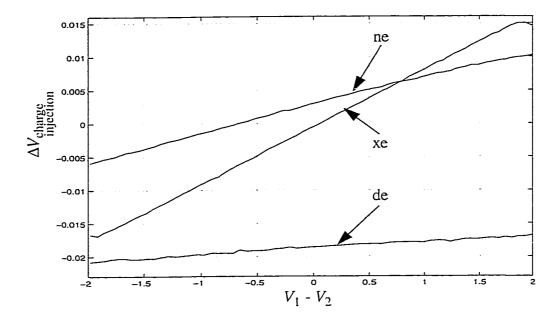

| Figure 5.16 | Slope effect on charge injection. 82                                                                                                                                                                                                        |

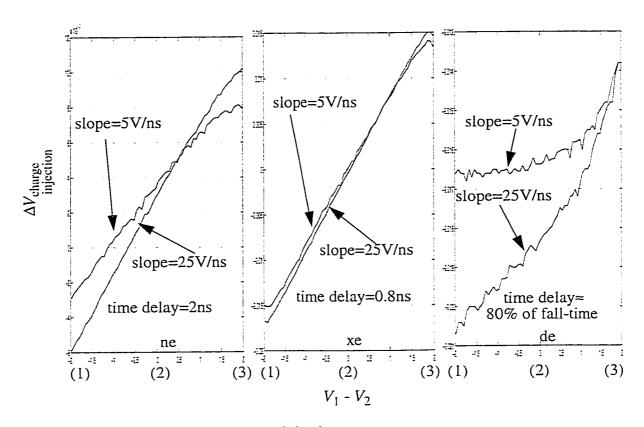

| Figure 5.17 | Time delay effect on charge injection. 83                                                                                                                                                                                                   |

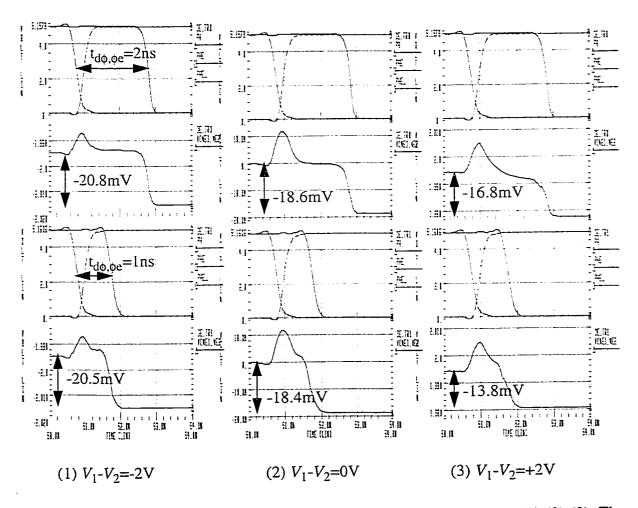

| Figure 5.18 | Comparison of the 1ns vs 2ns time delay curves in cases (1) (2) (3). The clock has a slope of 25V/ns with a time delay between $\phi_e$ and $\phi_{e}$ of 0.2ns measured at analog ground level ( $t_{d\phi e, \phi e} \approx 0.2$ ns). 84 |

| Figure 5.19 | Charge injection curves without early clock phases. 85                                                                                                                                                                                      |

| Figure 5.20 | The best case among the three switches studied is the dummy switch. 86                                                                                                                                                                      |

| Figure 5.21 | Typical two-phase non-overlapping clock generator. 87                                                                                                                                                                                       |

| Figure 5.22 | Four-phase non-overlapping clock generator. 88                                                                                                                                                                                              |

| Figure 5.23 | The whole clock generator. 89                                                                                                                                                                                                               |

| Figure 5.24 | Clock waveforms. 90                                                                                                                                                                                                                         |

| Figure A.1  | Symmetric floorplan for a fully differential SC circuit. 102                                                                                                                                                                                |

| Figure A.2  | Local symmetry floorplan for a fully differential SC circuit. 102                                                                                                                                                                           |

## **List of Abbreviations and Symbols**

a Clock slope

A Op-amp DC gain

α Feedforward coefficient

ADC Analog-to-digital Converter

β Feedback coefficient

B Vittoz switching parameter

BP $\Sigma\Delta$  Bandpass sigma-delta

$C_G$  Gate capacitance

C<sub>H</sub> Holding capacitor

C<sub>IN</sub> Op-amp input capacitance

CMFB Common-mode feedback

Cov Overlapping capacitor

$C_S$  Sampling capacitor

D/A Digital-to-analog

φ Clock phase

FE Forward Euler

f<sub>s</sub> Sampling frequency

g<sub>DS</sub> Drain-source conductance

GSM Global System for Mobile (cellphone)

k Quantizer gain

LDI Lossless discrete integrator

LP Lowpass

m Magnitude error

MASH Multi-stage noise shaping

NMOS n-channel Metal Oxide Semiconductor

NTF Noise transfer function

OSR Oversampling ratio

PMOS p-channel Metal Oxide Semiconductor

$\theta$  Phase error

Q<sub>ch</sub> Channel charge

R<sub>EO</sub> Equivalent resistance

R(z) Resonator transfer function

R<sub>ON</sub> The "ON" resistance of a switch

SC Switched-capacitor

$\Sigma\Delta$  Sigma-delta

S/H Sample-and-hold

SNR Signal-to-noise ratio

STF Signal transfer function

$\tau$  Time constant

t<sub>d</sub> Time delay

t<sub>onoff</sub> Time between a switch turns off and its dummy turns on

$\Delta V_{\mathrm{charge\ injection}}$  The error voltage due to charge injection

$V_{ON}$  The "ON" voltage of a CMOS device

$V_{sw}$  The switched voltage

$V_t$  Threshold voltage

X-gate Transmission gate

z complex frequency in Z-domain

# Chapter 1 Introduction

The most recent analog to digital (A/D) converter architecture, sigma-delta ( $\Sigma\Delta$ ), maximizes the "performance/cost" ratio of an integrated circuit (IC) design (provides high resolution without trimming or high precision components, and reduces the cost of the antialiasing filter), and also makes possible a cheap monolithic integration of a whole radio circuit. For example, a bandpass  $\Sigma\Delta$  modulator placed in the IF (intermediate frequency) stage of a radio reduces the stringency of specifications on the analog filters, and moves the digital signal processing closer to the front-end.

The key technical problem in this thesis is to use advanced circuit techniques and converter architectures to get high performance (in terms of speed, power, and resolution) from a low-cost technology. This work "scales" in the sense that it will guide later attempts to push more advanced technologies to their limits.

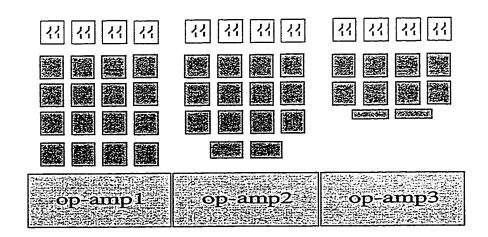

Combining the circuits designed in this thesis with architectural work [Brandt91, Lewis92] done by others, a modulator was designed and implemented in a  $1.5\mu m$  CMOS

process [Mitel1.5]. It is sixth order and uses a tri-level quantizer rather than the two-level structures generally used. The use of a double sampling technique reduced the clock frequency by half. A two-delay loop was implemented with a single op-amp, and consequently the modulator needed only three op-amps instead of six. The combination of the above represents a novel architectural solution which allowed the best possible performance out of a given process at the expense of increased difficulty in design.

#### 1.1 High-Order $\Sigma\Delta$ modulators

Because it is easier to understand and implement and it is always stable, the fourth order structure is preferred to higher orders in many practical applications of a bandpass  $\Sigma\Delta$  modulator [Jantzi93, Norman96, Song95]. But with an analysis of the instability and tonal behaviour, and with proper design, a robust sixth, or even higher order bandpass modulator can be obtained.

The main advantages that high-order  $\Sigma\Delta$  modulators offer are the high signal to noise ratios (SNR) for modest oversampling ratios and good tonal behaviour compared to low order modulators.

Since 1977, when Ritchie [Ritchie77] proved that a  $\Sigma\Delta$  modulator can be built with an order greater than two, their performance has significantly increased, and commercial ICs have been designed with as many as 24 bits of resolution [Fujimori97]. The main structure for implementation of high-order  $\Sigma\Delta$  modulators is the cascade of integrators with feed-

back signals from the digital to analog converter (DAC) at the input of each integrator to insure stability. Figure 1.1 shows this.

Figure 1.1 Single-loop high-order  $\Sigma\Delta$  modulator structure.

Another approach is the MASH (multi stage noise shaping) [Hayashi86, Longo88] structure, shown in Figure 1.2, that consists of two modulators, one for processing the signal and the other one to digitize the quantization noise of the first one. The digital outputs of the two modulators are combined such that the quantization error of the first stage is cancelled. The problem here is the matching required between the filters in the two loops, analog and digital, but stability is guaranteed (first and second order  $\Sigma\Delta$  modulators are inherently stable [Hein93]). Further improvement can be achieved if instead of a 1bit quantizer for the above high-order  $\Sigma\Delta$  modulator a multi-bit one is used [Larson89]. The multi-bit modulators reduce the amount of quantization noise resulting in a much simpler loop filter function. The difficulty here is given by the nonlinearity of the D/A (digital to analog) part of the quantizer, compared to the one-bit quantizer that can be implemented to be very close to ideal. A solution to DAC nonlinearity is the "dynamic element matching" (or capacitor shuffling) technique [Carley89, Galton95, Schreier96] that consists of randomizing or noise-shaping the digital to analog conversion error such that it looks like

noise and not harmonics. Consequently the harmonic distortion is reduced. Nevertheless, multi-bit modulators require a more complex decimation filter.

Figure 1.2 MASH  $\Sigma\Delta$  modulator structure.

#### 1.2 Clock Techniques

Given a particular CMOS technology, the performance of classical op-amps (DC gain, cutoff frequency, phase margin) is limited, and the design difficulty of such an op-amp depends on the particular circuit that it is used in. In switched-capacitor circuits one can exploit the fact that, sometimes, the op-amp isn't used on both phases of the clock. One can therefore double the sampling frequency by finding a circuit architecture where the op-amp processes signals on both clock phases.

Many switched-capacitor (SC) circuits known in the literature work as follows: a capacitor is charged from the input signal on phase 1 of the clock, and on phase 2 is discharged to create a signal sample at the output of an op-amp. The only thing that the op-amp did on

phase 1 was to store a previous charge, or worse yet, it did nothing. Figure 1.3.a shows such a circuit.

An efficient way to double the speed of SC circuits without imposing any other requirements on op-amps is the double-sampling technique, as shown in Figure 1.3.b. This implies the use of two capacitors such that, e.g. on phase 1 of the clock, one capacitor is charged from the input signal, and the other one is discharged to create a sample at the op-amp output. Phase 2 it is the same except that the two capacitors exchange their roles. The trade-off is that harmonic distortion is introduced due to mismatch paths.

Figure 1.3 Typical a) single-sampled integrator, b) double-sampled integrator.

#### 1.3 Thesis Outline

The next chapter is a review of existing  $\Sigma\Delta$  modulator architectures and their constituent cells (or block components). Their advantages and disadvantages are shown, along with critical non-ideal effects and source of errors.

The noise transfer function (NTF) and signal transfer function (STF) for a sixth-order BP $\Sigma\Delta$  (bandpass sigma-delta) modulator are studied and designed in chapter 3, and a novel architecture is proposed. Novel contributions of this thesis and their effects on the architecture's performance are presented next. The modulator architecture consists of a cascade of resonators that, in order to increase the bandwidth for a given OSR, has the feature of splitting the NTF zeros along the tangent to the unit circle, rather than along the unit circle. These zeros, because they are slightly outside the unit circle, will introduce a small amount of chaos into the modulator [Schreier93] and improve its tonal behaviour. A tri-level quantizer is used along with the SC four-phase sampling technique. The novelty consists in combining the double-sampling technique, the NTF zeros splitting technique and the tri-level quantizer. These innovations improve the SNR and the stability.

Chapter 4 deals with the circuit implementation. A new four-phase SC resonator is proposed together with a study of the component circuits (op-amps, quantizer, comparator, etc.). The resonator's novel structure doubles the sampling frequency without increasing the demands on op-amp performance.

By reason of charge injection effects, switch design is critical at high clock rates. Because sampling occurs at both ends of the sampling capacitors the conventional "bottom-plate sampling" approach is inapplicable. Therefore we have to investigate new ways to minimize charge injection effects. These effects are thoroughly studied in chapter 5. The transmission gate (X-gate), the NMOS switch, and the NMOS with dummy switches are

compared. The NMOS with dummy switch is proposed for the implementation of  $\Sigma\Delta$  modulator circuit. The clock generator is also presented in this chapter.

Appendix A shows some practical problems in designing an SC circuit layout, and how to solve them. Only a carefully designed layout can ensure IC functionality close to the simulated behaviour. A chip has been submitted for fabrication (details in summary and final conclusions chapter 6).

# Chapter 2 The State of the Art

The design of  $\Sigma\Delta$  modulators relies on basic circuits like delay cells to implement integrators or resonators as building blocks. An integrator can be realized, when using a SC structure, by feeding back the output of a one-delay cell to its input. This way of realising an integrator offers innovative design solutions as compared to the one-op-amp-feedback-capacitor integrator. By using two delays and feeding back the inverted output, a resonator is obtained. Integrators are used to design lowpass  $\Sigma\Delta$  modulators, and resonators for bandpass.

#### 2.1 BP $\Sigma\Delta$ , High-Order, (1.5 $\mu$ m CMOS)

The robust SC circuit technology was chosen for the sixth order modulator design in this thesis, due to its compatibility with standard double-poly CMOS processes. The *NTF* pole and zero locations are set by capacitor ratios, which are highly accurate (0.1% to 1%) [Lakshmikumar86]. In SC circuits, as long as full signal settling occurs, the exact shape of

op-amp settling doesn't matter, thus clock jitter is negligible except at the system input. By careful design and optimization, effects like  $\frac{kT}{C}$  noise, aliasing of out-of-band noise because of the sampling nature of the SC circuits, and large spike currents drawn by the capacitors, can be diminished.

#### 2.1.1 Topologies

A  $\Sigma\Delta$  converter is characterized by two transfer functions: the noise transfer function (NTF), and the signal transfer function (STF). The number of topologies for a  $\Sigma\Delta$  modulator is given by the number of ways you can build a filter corresponding to the required NTF and STF. Theoretically, this number is infinite.

Figure 2.1 Structure of  $\Sigma\Delta$  modulator (linear model).

By choosing the desired *NTF* for a particular application, one can verify that the *STF* shares poles with the *NTF*. The equations of these transfer functions are

$$NTF = \frac{Y}{Q}\Big|_{U=0} = \frac{1}{1+H(z)}$$

EQ 2.1

$$STF = \frac{Y}{U}\Big|_{Q=0} = \frac{G(z) \cdot H(z)}{1 + H(z)}$$

EQ 2.2

The NTF is defined by H(z), but the STF depends also on G(z). The noise transfer function notch depth and its out-of-band gain are defined by the pole and zero locations. Once those are set, the remaining degree of freedom for the signal transfer function is adjusted by G(z). Depending on the modulator architecture, sometimes G(z) is 1. Then the STF zeros are determined only by H(z), and the STF cannot be controlled independently of the NTF. This is not too stringent, because the main requirement for the STF is to be flat over the band of interest.

Some BP $\Sigma\Delta$  topologies from the literature are presented next, where the modulator's band of interest is centered around  $\pi/2$ , or a quarter of the sampling frequency. Their lowpass versions can be obtained by replacing the resonators with integrators. The feedforward and feedback coefficients, and the numerators of the resonator gain can generally be considered to be of the form  $Cz^{-n/2}$ , where C is a constant, and n is an integer.

#### 2.1.2 Cascade of Resonators with Feedforward Summation

For this type of structure, shown in Figure 2.2, the modulator has transfer functions given by EQ 2.3 and EQ 2.4, where N is the number of resonators.

$$NTF = \frac{(1+z^2)^N}{(1+z^2)^N - \alpha_1(1+z^2)^{N-1} - \alpha_2(1+z^2)^{N-2} - \dots - \alpha_N}$$

EQ 2.3

$$STF = \frac{\alpha_1(1+z^2)^{N-1} + \alpha_2(1+z^2)^{N-2} + \dots + \alpha_N}{(1+z^2)^{N-1} - \alpha_1(1+z^2)^{N-1} - \alpha_2(1+z^2)^{N-2} - \dots - \alpha_N}$$

EQ 2.4

Figure 2.2 Cascade of resonators with feedforward coefficients.

The noise transfer function has all its zeros at  $\pi/2$ , with their conjugates at  $3\pi/2$ , or  $z=\pm j$ . In the design process, all the  $\alpha$  coefficients are defined by the *NTF* only, and therefore the *STF* will be fixed.

# 2.1.3 Cascade of Resonators with Feedforward Summation and Local Resonator Feedback Coefficient [Welland89]

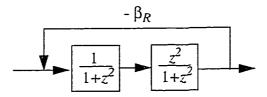

The difference between this topology and the previous one is the small coefficient,  $-\beta_R$ , around a pair of resonators, as shown in Figure 2.3.

Consider a loop of resonators with the small feedback  $-\beta_R$ , where one of the resonators has

gain

$$\frac{z^2}{1+z^2}$$

, as shown in Figure 2.4.

This is a bandpass version of an "LDI-phased" resonator[Singor94]. The overall Z-domain function is:

Figure 2.3 Cascade of resonators with feedforward summation and local resonator feedback coefficient.

Figure 2.4 Cascade of resonators.

$$R(z) = \frac{z^2}{z^4 + (2 + \beta_R)z^2 + 1}$$

EQ 2.5

The NTF zeros, which are the poles of R(z), are split along the unit circle around  $\pi/2$  with an angle equal to  $0.5 \cos^{-1}(1+\beta/2)$ . Coupling resonators this way in a BPSA modulator will spread the NTF zeros around the band of interest, such that there will be an improvement in SNR of several decibels [Jantzi91].

Figure 2.5 The NTF zeros split a) along the unit circle, b) along the tangent to the unit circle.

If both of the resonators have two delays, as in Figure 2.3, then the *NTF* zeros are split along the tangent to the unit circle at  $\pi/2$ , and this case will be studied in detail in chapter 3. Figure 2.5 shows the way in which the *NTF* zeros can split.

# 2.1.4 Cascade of Resonators with Distributed Feedforward, Feedback and Local Resonator Coefficients

With this type of structure, shown in Figure 2.6, the designer can choose the STF zeros independently of the NTF [Chao90]. The feedback coefficients are given by the desired noise transfer function, and the feedforward ones are calculated to flatten the signal transfer function over the band of interest, and attenuate as much as possible the out-of-band noise. The small coefficients,  $\beta_R$ , of the local resonators split the noise transfer function's zeros along the tangent to the unit circle. The NTF and STF have the following general form:

$$NTF = \frac{(1+z^2)^N - (\beta_{R1} + \beta_{R2} + \dots)(1+z^2)^{N-2}}{(1+z^2)^N - \beta_1(1+z^2)^{N-1} - \dots - \beta_{N-2}(1+z^2)^2 + (\beta_{N-1} + \beta_{R1} + \beta_{R2} + \dots)(1+z^2) + \beta_N} \quad EQ \ 2.6$$

$$STF = \frac{\alpha_1 + \alpha_2(1+z^2) + \dots + \alpha_N(1+z^2)^{N-1}}{(1+z^2)^N - \beta_1(1+z^2)^{N-1} - \dots - \beta_{N-2}(1+z^2)^2 + (\beta_{N-1} + \beta_{R1} + \beta_{R2} + \dots)(1+z^2) + \beta_N} \quad EQ 2.7$$

Figure 2.6 Cascade of resonators with distributed feedforward, feedback and local resonator coefficients.

#### **2.2** Delay Cells for $\Sigma\Delta$

SC circuits operate in discrete time, sampling an analog signal and then processing these samples. An arbitrary transfer function can be made by interconnecting weighted sums of unit delays,  $z^{-1}$ . An op-amp and at most a couple of capacitors can be sufficient to implement such a delay.

#### 2.2.1 Half Delay Cell

There are many ways that a half delay cell can be realized. By using a two-phase non-overlapping clock, a half delay is obtained if on phase 1 the input signal is sampled, and on phase 2 the sample is delivered to the output. A particular delay circuit configuration is chosen depending on its sensitivity to non-ideal effects.

Two examples of half-delay cells are shown in Figure 2.7. The circuits are single ended to show the idea, but fully differential versions are generally used [Gregorian81, Hsieh81, Haug85, Ribner85, Roberts86].

Figure 2.7 SC half-delay circuits: a) offset cancelled, b) capacitor mismatch insensitive.

The circuit type of Figure 2.7.a is used when offset-cancelling is needed (e.g. in lowpass  $\Sigma\Delta$  modulators). On phase 1 the sampling capacitor  $C_S$ , charges to  $(V_{in}-V_{off})$ , where  $V_{in}$  is the input voltage and  $V_{off}$  is the op-amp offset. On phase 2 the charge transferred on the holding capacitor is  $C_S(V_{in}-V_{off})+C_SV_{off}$ . The  $V_{off}$  term cancels out and the output voltage doesn't depend on op-amp offset. If  $C_S=C_H$ , the gain of this circuit is  $z^{-1/2}$ . If we assume a finite op-amp DC gain, A, then the circuit's gain is given by the formula:

$$G(z) = \frac{C_S}{C_H} \cdot \frac{1}{1 + \frac{C_H + C_S + C_{IN}}{A \cdot C_H}} \cdot z^{-1/2}$$

EQ 2.8

where  $C_{IN}$  is the sum of the parasitic capacitances at the op-amp input, plus the internal op-amp input capacitance.

The half-delay cell of Figure 2.7.b is a capacitor-mismatch insensitive circuit. It flips the same capacitor  $C_S$  from the input to the output, and this means a perfect match between the two voltage samples. If one takes into account the finite op-amp DC gain, A, the circuit's gain is:

$$G(z) = \frac{1}{1 + \frac{C_S + C_{IN}}{A \cdot C_S}} \cdot z^{-1/2}$$

EQ 2.9

Comparing EQ 2.8 to EQ 2.9, the conclusion is that the delay cell of figure b) is less sensitive to finite op-amp DC gain.

#### 2.2.2 Full Delay Cell

Figure 2.8 shows a one-delay cell using a single op-amp and three capacitors [Longo93]. On phase 1,  $C_S$  is charged from the input voltage, on phase 2 this charge is transferred to  $C_I$ , and on next phase 1,  $C_I$  transfers its charge to the holding capacitor  $C_H$ . The capacitor  $C_I$  is used to transfer the charge from  $C_S$  to  $C_H$ , and its value is solely defined by the op-amp swing and settling and thermal noise considerations.

Figure 2.8 A full-delay sample and hold.

If we don't take into account the nonideal effects, the gain of the circuit is:

$$G(z) = \frac{C_S}{C_H} \cdot z^{-1}$$

EQ 2.10

The finite op-amp DC gain and the non-zero input capacitance  $C_{IN}$ , introduce in the gain G(z) an error component in both magnitude (m) and phase  $(\theta)$  [Bazarjani96]. The gain formula that shows this, is

$$G(z) = \frac{C_S}{C_H} \cdot z^{-1} \cdot \{m \cdot e^{j\theta}\} \qquad where$$

EQ 2.11

$$m = 1 - \frac{1}{A} \left( \frac{C_I + C_S + C_{IN}}{C_I} + \frac{C_H + C_I + C_{IN}}{C_H} \right) + \frac{\cos \frac{\omega T}{2}}{A} \left( 2 + \frac{C_{IN}}{C_I} + \frac{C_{IN}}{C_H} \right)$$

EQ 2.12

$$\theta = -\frac{\sin\frac{\omega T}{2}}{A} \left( 2 + \frac{C_{IN}}{C_I} + \frac{C_{IN}}{C_H} \right)$$

EQ 2.13

For example, if  $A=50 \, \mathrm{dB}$ ,  $C_I=C_S=C_H=C_{IN}$ , and at frequency  $\mathrm{f_s}/4$  where the passband is centered, we have m=0.990 and  $\theta=-0.0089$ . Therefore, for the full delay cell, a 50 dB DC gain op-amp causes a 1% gain error and 0.89% phase error.

#### 2.3 Double-Sampling S/H

Figure 2.9 shows a double sampling circuit derived from the single-sampled version of Figure 2.7.b.

Figure 2.9 A full-delay double-sampling S/H (sample and hold).

$C_{S1}$  and  $C_{S2}$  exchange their roles on each phase of the clock. As a result, an output sample is available on both phases. The maximum sampling frequency for this circuit is given by  $1/T_{\text{settle}}$ , where  $T_{\text{settle}}$  is the op-amp settling time. This sampling rate is twice as fast as the single-sampled S/H of Figure 2.7.b.

A limitation of this type of circuit is that finite op-amp gain combined with non-zero input capacitance  $C_{IN}$  causes magnitude and phase error in the output signal. This is due to the charge stored by the input capacitance at the end of each phase. Because the charge is conserved on the op-amp input node this charge contributes to the output on the next phase.

Using the double sampling technique, a second signal path is introduced. Mismatch between the two paths causes an inband image of the signal [Hurst90]. This can be reduced if architectural solutions are explored as in [Hurst92].

#### 2.4 Switches and Charge Injection

The accuracy of SC circuits is limited due to charge injection [Gray80]. When the switch is on, it connects the signal-source node to the data-holding node, represented by the capacitor  $C_H$  of Figure 2.10. When the switch turns off, a significant part of the charge stored in the transistor channel is transferred to the holding capacitor, creating an error component,  $\Delta V$ , in the voltage sample. Other parts of the channel charge go to the source and to the substrate.

Figure 2.10 One-switch sample and hold circuit.

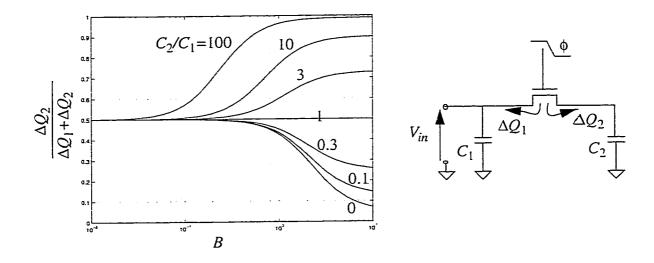

If the channel carrier intrinsic transient time is much smaller than the clock transient fall time, then the charge flow to the substrate is unsubstantial. The carrier intrinsic transient time is on the order of the gate capacitance times the on-resistance of the channel. Practical values for this are fractions of nanoseconds. The channel charge distribution between source and drain depends on the total values of  $C_S$  and  $C_H$  [Vittoz85], the fall-time of the clock, and also on the input source resistance [Shieh87]. For a slow fall time, the potential of the source and drain will be equalized, and the amount of charge on each side strongly depends on their impedances: more charge will leak into the low impedance side. For a fast clock the channel charge is equally distributed to both sides of the switch [Wegmann87]. If we define B, the switching parameter, as in EQ 2.14 below, then the dependence of the amount of injected charge on B is depicted in Figure 2.11.

Figure 2.11 Vittoz curves.

$$B = (V_{DD} - V_{in} - V_t) \sqrt{\frac{\beta}{aC_2}} \qquad where \qquad \beta = \mu C_{ox} \frac{W}{L} \qquad and \qquad a = slope(V/ns) \quad \text{EQ 2.14}$$

Taking into account that the channel charge is  $Q_c = C_{ox}WL(V_{GS} - V_t)$ , and only a fraction  $\alpha$  is transferred to the drain, the voltage across the holding capacitor is  $V_{out} = V_{in} - \Delta V$  or:

$$V_{out} = V_{in} - \alpha \frac{C_{ox}WL(V_{DD} - V_{in} - V_t)}{C_H}$$

EQ 2.15

$\Delta V$  is the accuracy error from the ideal of  $V_{out} = V_{in}$ .

To diminish the effects of charge injection, different type of switches and techniques can be used:

- 1. NMOS switches for low voltages, PMOS for high voltages, and transmission-gates (complementary switches) for voltages around  $V_{DD}/2$  (this reduces the charge injection by minimizing the sizes of switches needed)

- 2. dummy switches for signal dependent charge injection [Eichenberger89]

- 3. bottom plate sampling [Gregorian86] with an early version of the clock signal

- 4. and, as a general rule, choose the minimum size switch that satisfies the settling requirements

These will be studied in chapter 5.

### 2.5 Conclusions

This chapter discussed several structures for BP $\Sigma\Delta$  modulators and formulae for their transfer functions were provided. The cascade of resonators topology with distributed feedforward, feedback and local resonator coefficients allows one to design the *STF* independently of the *NTF*. The function of the local resonator is to split the *NTF* zeros in the band of interest thereby improving SNR by several dBs.

$\Sigma\Delta$  modulator building blocks were presented and, taking into account circuit non-idealities, their gain formulae were given.

Charge injection was outlined and the way it influences circuit performance was presented. A brief list of possible solutions to charge injection effects was given.

## Chapter 3 The $\Sigma\Delta$ Design

Two questions that have no precise answer concern the idle tones and the stability of a  $\Sigma\Delta$  modulator. For low-order  $\Sigma\Delta$  modulators the main limitations are due to idle tones and low theoretical SNR, and for high-order modulators there are more sources of error due to circuit complexity, and/or the stability is critical. Practical implementations for lowpass second to sixth order, and second to sixth order bandpass  $\Sigma\Delta$  modulators have been reported [Feldman98, Hairapetian96].

Although the sampling frequency is limited by the given process, using the high-order approach helps increase the SNR and/or the bandwidth of the  $\Sigma\Delta$  modulators, and the idle tones are also reduced close to the noise floor level or even below.

The modulator of this thesis is intended to work at a sampling frequency of 20MHz (limited to this value by the slow 1.5µm CMOS process) and for a bandwidth of 200kHz (proper for GSM or FM broadcast specifications). This results in an oversampling ratio (OSR) of 50.

#### 3.1 SNR vs OSR

Table 3.1 presents the performance of other SC bandpass (BP) or lowpass (LP)  $\Sigma\Delta$  modulators of different orders and using different number of quantizer levels (Q-levels). We can notice the complexity vs performance trade-off. The performance was improved by increasing the order of the modulator and/or the number of quantizer levels, which translates into increasing the circuit complexity. Increasing the oversampling ratio is not always a solution because of the limited clock frequency in a given process.

Table 3.1 Complexity vs performance of other art.

| Order-<br>Type | Q-<br>levels | SNR<br>(dB) | OSR | BW<br>(kHz) | f <sub>s</sub><br>(MHz) | V <sub>DD</sub><br>(V) | CMOS<br>process | paper           |

|----------------|--------------|-------------|-----|-------------|-------------------------|------------------------|-----------------|-----------------|

| 4-BP           | 2            | 72          | 200 | 200         | 80                      | 3.3                    | 0.6μm           | [Ong97]         |

| 6-BP           | 2            | 62          | 32  | 200         | 13                      | 3                      | 0.8µm           | [Hairapetian96] |

| 3-LP           | 9            | 79          | 25  | 100         | 5                       | 2.7                    | 0.6μm           | [Yasuda98]      |

| 4-LP           | 2            | 90          | 24  | 1000        | 48                      | 5                      | lμm             | [Marques98]     |

| 4-LP           | 16           | 78          | 16  | 250         | 8                       | 5                      | 1.2µm           | [Baird96]       |

| 6-LP           | 2            | 72          | 16  | 700         | 22.4                    | 3.3                    | 0.72µm          | [Feldman98]     |

| 6-BP           | 3            | >90         | 50  | 200         | 20                      | 5                      | 1.5µm           | this thesis     |

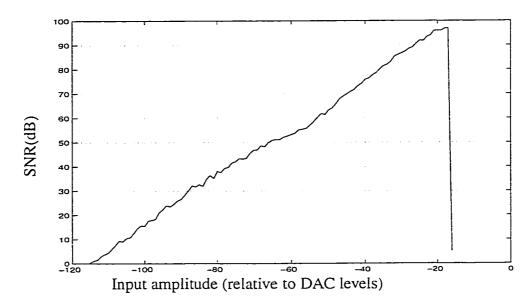

Figure 3.1 shows SNR vs OSR curves collected from previous simulation results [Singor94]. They are for bandpass high-order  $\Sigma\Delta$  modulators of order 4, 6, and 8 that use either a two-level or a tri-level quantizer. For oversampling ratios around 50, the 6<sup>th</sup> order tri-level quantizer  $\Sigma\Delta$  modulator gives a signal-to-noise ratio comparable to the 8th order two-level one. This SNR value is around 90 dB. These curves were found for optimized

noise transfer functions with zeros placed across the band of interest [Ouslis90, Jantzi91].

The gain in SNR due to the optimized placement of zeros is several decibels.

Figure 3.1 SNR versus oversampling ratio of a  $4^{th}$ ,  $6^{th}$ , and  $8^{th}$ -order  $\Sigma\Delta$  modulator with a 2, respectively tri-level quantizer.

## 3.2 NTF, STF Design

From the previous section, from circuit complexity reduction considerations, the order of the modulator has been chosen to be six. The next step is to find the noise transfer function, as it is the function that will determine the SNR, and finally the signal transfer function will be set to the extent of its remaining degrees of freedom.

The noise transfer function design is restricted by causality and stability constrains. The system is causal if the loop around the quantizer doesn't contain any delay-free loops. This means that the loop gain,  $H(z) = \frac{1}{NTF} - 1$ , (see Figure 2.1, and EQ 2.1) must have at

least a  $z^{-1}$  delay, or its first discrete-time impulse response must be at  $t \ge 1$  [Adams91].

This further implies that  $\lim_{z \to \infty} H(z) = 0$ , or  $\lim_{z \to \infty} NTF = 1$  [Jantzi93]. Increasing the

notch depth the NTF out-of-band gain accordingly increases, as shown in Figure 3.2.

Figure 3.2 SNR vs *NTF*'s out-of-band gain for a  $6^{th}$ -order tri-level quantizer  $\Sigma\Delta$  modulator(OSR=50).

If the noise transfer function out-of-band gain is high, the quantizer input becomes large, and consequently the quantizer gain drops (because the quantizer output levels are fixed, 0 or  $\pm 1$ , while its input is increasing). This moves the *NTF* poles outside the unit circle and makes the modulator unstable [Ritoniemi90]. Due to the "pushing to the limits" nature of this thesis, the noise transfer function out-of-band gain has been chosen to be 7 dB. A small margin of safety was still maintained such that the high-risk stability edge is 1.5dB of dB away.

#### 3.2.1 Lowpass to Bandpass Transformation

A convenient way to design a bandpass  $\Sigma\Delta$  modulator is to design first a lowpass modulator, and then map its poles and zeros from DC to  $\pi/2$  and  $3\pi/2$  using the transformation  $z^{-1} \rightarrow -z^{-2}$ . There are other similar transformations [Oppenheim89], but this one offers the advantage that it preserves the lowpass properties and performance (linearity, stability, SNR), and having the passband placed at  $f_s/4$  allows for innovation in system design.

As discussed in chapter 2, the zeros of the noise transfer function are distributed through the signal band to lower the inband noise. FiltorX [Ouslis90] was used to optimally place the poles and zeros for both NTF and STF. The "least-p<sup>th</sup>" optimizer of filtorX adjusted the poles and zeros of NTF and STF such that their amplitude responses closely match the measures of ideality that we defined. These measures of ideality were set along the inband and out-of-band Z-plane contours and were individually weighted for their importance to the overall optimization. Figure 3.3 shows the result plots in Matlab [Matlab], and EQ 3.1 and EQ 3.1 represent the Z-domain transfer functions with precise coefficients.

$$NTF = \frac{b_0 + b_2 z^{-2} + b_4 z^{-4} + b_6 z^{-6}}{d_0 + d_2 z^{-2} + d_4 z^{-4} + d_6 z^{-6}}$$

where  $b_0 = 1$  and  $d_0 = 1$  EQ 3.1

$$b_2 = 2.99403$$

$$d_2 = 1.54064$$

$$d_4 = 0.990024$$

$$d_6 = 0.996541$$

$$d_6 = 0.146315$$

$$STF = \frac{a_0 + a_2 z^{-2} + a_4 z^{-4} + a_6 z^{-6}}{d_0 + d_2 z^{-2} + d_4 z^{-4} + d_6 z^{-6}} \qquad where \qquad a_0 = 0 \qquad and \qquad d_0 = 1 \qquad EQ \ 3.2$$

$$a_2 = -0.501538 \qquad d_2 = 1.54064$$

$$a_4 = -0.81582 \qquad d_4 = 0.990024$$

$$a_6 = -0.617331 \qquad d_6 = 0.146315$$

Figure 3.3 The magnitude of the  $6^{th}$ -order *NTF* and *STF*, obtained from filtorX, with their poles and zeros.

The STF couldn't be made more selective, therefore a narrow IF filter in front of the modulator will be required for FM radio applications.

## 3.3 Cascade of SC Resonators Structure

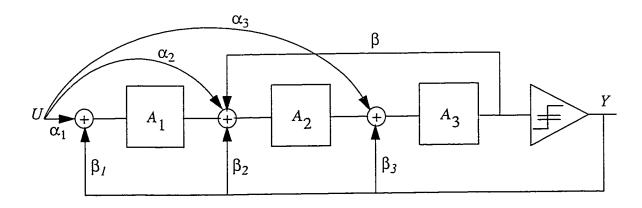

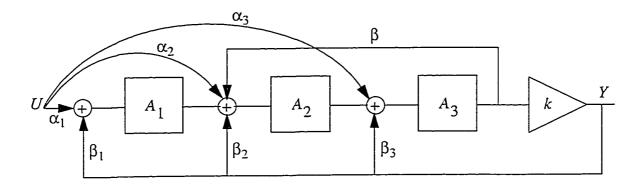

Comparing different types of single loop architectures (see section 2.1.1), the one of Figure 2.6 was the most beneficial in this case. Its advantages include splitting the NTF's zeros across the passband, and the degree of freedom that allows us to flatten the STF in the band of interest by choosing appropriate feedforward coefficients  $\alpha$ . Figure 3.4 shows

the block diagram of the BPS $\Delta$  modulator, where  $A_1$ ,  $A_2$ ,  $A_3$  are resonators with gain  $\left(\frac{1}{1+z^2}\right)$ .  $A_2$ ,  $A_3$  and  $\beta$  together give a transfer function

$$R(z) = \frac{1}{z^4 + 2z^2 + 1 + \beta}$$

EQ 3.3

The noise transfer function zeros, which are the poles of R(z), are split along the tangent to the unit circle around  $\pi/2$  and  $3\pi/2$  with an angle equal to  $\Delta\theta$  each side (EQ 3.4).

$$\Delta\theta = \frac{1}{2} a\cos\left(\frac{1}{\sqrt{1-\beta}}\right)$$

EQ 3.4

Splitting the zeros brings an improvement in SNR of several dBs, and the fact that the zeros are slightly outside the unit circle makes the system chaotic [Schreier93]. This, in general, reduces the inband idle tones.

Figure 3.4 Block diagram of the  $6^{th}$ -order bandpass  $\Sigma\Delta$  modulator.

#### 3.3.1 NTF, STF equations

The noise and signal transfer functions of the modulator of Figure 3.4 are:

$$NTF = \frac{1 - \beta A_2 A_3}{1 - \beta_1 A_1 A_2 A_3 - (\beta_2 + \beta) A_2 A_3 - \beta_3 A_3}$$

EQ 3.5

$$STF = \frac{\alpha_1 A_1 A_2 A_3 + \alpha_2 A_2 A_3 + \alpha_3 A_3}{1 - \beta_1 A_1 A_2 A_3 - (\beta_2 + \beta) A_2 A_3 - \beta_3 A_3}$$

EQ 3.6

Notice here that if  $A_1$ ,  $A_2$ ,  $A_3$  are integrators  $\left(\frac{1}{1-z}\right)$ , the modulator is lowpass. Identifying the expressions of *NTF* and *STF* obtained from filtorX (EQ 3.1, EQ 3.1) with the ones of EQ 3.5, EQ 3.6, the values of the feedback and feedforward coefficients were found:

$$\alpha_1 = -0.303053$$

$\beta_1 = 0.303076$   $\beta = -0.0025$   $\alpha_2 = 0.18726$   $\beta_2 = -0.90625$  EQ 3.7  $\alpha_3 = -0.501538$   $\beta_3 = 1.4534$

The small coefficient  $\beta$  was calculated by making the angle of EQ 3.4 equal to  $\frac{\pi}{125}$  as in the numerator of EQ 3.1. This is shown in Figure 3.5.a. Due to its small value,  $\beta$  was implemented as a T capacitor as in Figure 3.5.b. Its accuracy is not critical, and simulations show that the modulator's SNR changes negligibly if  $\beta$  is off by 25%. Even 50% error in  $\beta$  degrades the SNR by only a couple of dBs. Therefore it is believed that the parasitic capacitances will not have significant effects.

Figure 3.5 a) The NTF zero locations around  $\pi/2$ ; b) implementation of the capacitor corresponding to  $\beta$  = -0.0025

#### 3.3.2 Stability by root locus

A high-order single-loop modulator is prone to instability. A method to investigate the stability of a  $\Sigma\Delta$  modulator is the "root locus" method [Stikvoort88]. It consists of modelling the quantizer with a variable gain, k, as shown in Figure 3.6, and then analysing the root locus of the denominator D(z) of the transfer function Y/U, that is given by EQ 3.8.

$$D(z) = z^{3} + (k\beta_{3} - 3) \cdot z^{2} + (3 - 2k\beta_{3} - k\beta_{2} - \beta) \cdot z + k\beta_{3} + k\beta_{2} + k\beta_{1} + \beta - 1 \quad EQ 3.8$$

Figure 3.6 Single loop  $\Sigma\Delta$  modulator with the quantizer modelled as variable gain.

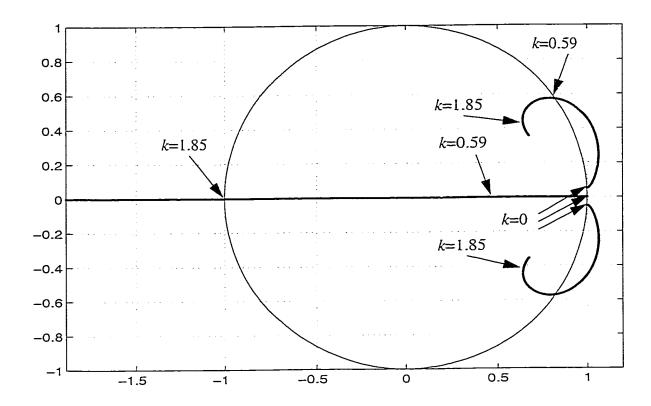

Taking into account the inherited properties of  $\Sigma\Delta$  when transforming from lowpass to bandpass using  $z^{-1} \to -z^{-2}$ , the stability analysis was done for the lowpass version of the modulator. The results are presented in Figure 3.7.

For k > 0.59 the complex roots move inside the unit circle, in other words the modulator model is stable. If k becomes too large (k > 1.85), then the real root will go outside the unit circle, accordingly the input to the quantizer will increase, and this means decreasing the effective quantizer gain, k, which will moves the root back inside the unit circle. This leads to stable operation of the modulator.

In the other case, when k < 0.59, the input to the quantizer becomes large, and this will move the complex conjugate roots outside the unit circle. The input to the quantizer will become larger and the modulator goes unstable.

For stability reasons k should be greater than 0.59. The value k = 1.85 is irrelevant since the modulator recovers by itself to a stable state whenever k > 1.85.

Figure 3.7 Root locus of the third order lowpass  $\Sigma\Delta$  modulator.

Hence the root locus indicates that a modulator remains stable as long as the quantizer input is not too large. Simulations showed that the maximum input level to the system should be less than approximately 0.3 (-10dB) relative to the DAC feedback level of 1 (a safety margin was taken into account, the actual number is approximately 0.45 or -7dB).

#### 3.3.3 Simulation Results

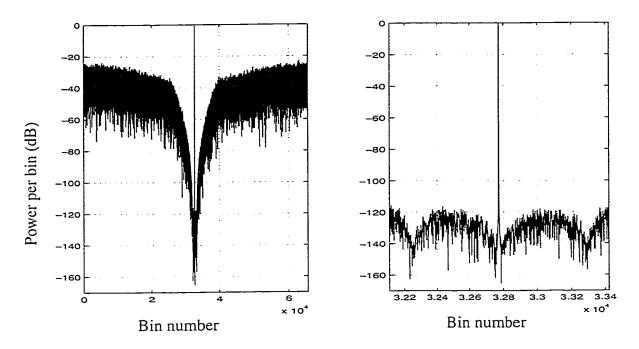

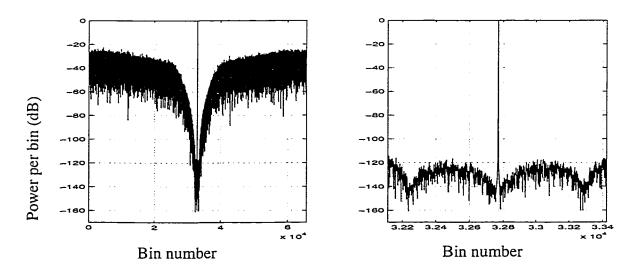

For a better accuracy, 131k points were used to plot the graphs of this section (an enhanced spectral resolution can reveal more tones because the noise floor is lowered). Figure 3.8 shows the typical output spectrum of the modulator. The right-hand side graph

shows the inband portion of the spectrum that contains 1310 points (corresponding to an OSR of 50). The input signal is a tone at -20dB relative to the DAC levels applied off center in the passband. (Notice here the three notches of the inband spectrum due to the three zeros of the modulator's *NTF*).

Figure 3.8 131k points whole and inband spectra with input tone near  $f_s/4$ .

The curve of Figure 3.9 shows how SNR varies with the modulator's input signal. At around a -60dB input signal the SNR curve exhibits a slightly nonlinearity. This is attributed to the tonal behaviour of the modulator [Gray90]. Discrete tones in any spectrum corresponds to time periodicity, therefore it is logical to relate tones in  $\Sigma\Delta$  modulators to their limit cycle behaviour. If a limit cycle is long enough, it will have power in the band-of-interest. The tones frequency is proportional to the input signal level. The amplitude of a tone is inversely proportional to the oversampling ratio. For small input signals, around

$u_{max}/OSR$  ( $u_{max}$  is the maximum amplitude of the input signal just before the modulator goes unstable), the idle tones lie the band-of-interest and degrade the SNR.

Figure 3.9 SNR vs input signal level for a bandwidth of 200kHz if clocked at 20MHz.

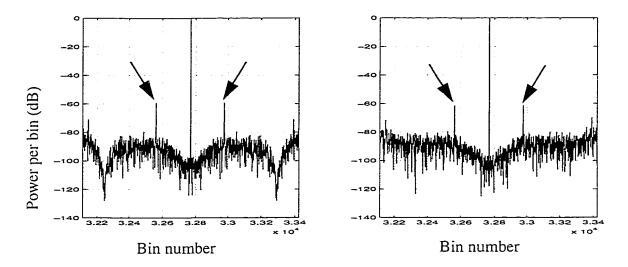

Because the high-order  $\Sigma\Delta$  modulators are less prone to idle tones than the low-order ones, it is difficult to see an improvement in the tonal behaviour of a sixth-order BP $\Sigma\Delta$  modulator if the *NTF*'s zeros are just slightly outside the unit circle. Figure 3.10 shows the spectra of two sixth-order modulators, one with all zeros on the unit circle, and the other one with the split zeros pushed outside the unit circle (1.0053 absolute value as compared to 1.00125 for our designed modulator). The location of the zero at  $f_s/4$  wasn't changed. The input signal is -60dB (where the inband tonal behaviour is most noticeable) and perfectly centered in the passband. The tones are (barely noticeable) smaller for the case with zeros outside the unit circle, and, as expected, the SNR dropped from 54.2dB (as in the "all unit circle zeros" case) to 53.4dB. This shows that splitting the poles outside the unit circle

doesn't significantly improve the tonal behaviour (improved already by choosing a high-order modulator), and the main purpose of this technique is to increase the bandwidth of interest (as initially considered). A bigger zero scaling (1.05) is necessary to suppress the tones below the noise floor [Risbo95], but this drastically reduces the SNR and the modulator becomes too unstable for any practical purpose.

Figure 3.10 Tonal behaviour for an input of -60dB relative to DAC levels (*NTF*'s zeros are on the unit circle for the left-hand side inband spectrum, and outside the unit circle for the right-hand side one).

Figure 3.11 Whole and inband spectrum for 1% mismatch coefficients.

Matlab simulations (with 131k points) showed that 1% coefficient mismatches don't significantly affect the modulator's SNR. Figure 3.11 shows the spectrum of a modulator that has coefficients off by 1%. The SNR barely change from 96.5dB, as in Figure 3.8, to 96.3dB.

#### 3.4 Conclusions

In this chapter the order, the *NTF*, the *STF*, and the structure of the modulator were determined according to the modulator's specifications (90dB SNR in the 200kHz band of interest, with a 20MHz maximum sampling frequency in the given technology) and it was shown to have stability and good tonal behaviour. Thus a sixth order, single loop, bandpass  $\Sigma\Delta$  modulator with a tri-level quantizer was designed from its third order lowpass equivalent.

The SNR of the modulator was increased several dBs by splitting the *NTF*'s zeros in the band of interest. Simulation results showed that the designed modulator loses little SNR if the coefficient mismatches are as large as 1%, except the small coefficient  $\beta$  of the loop of resonator that can vary as much as 25%.

Chaos is not much of an issue at this level, nevertheless it was introduced in the modulator at no expense.

# Chapter 4 The $\Sigma\Delta$ Circuit Implementation

$\Sigma\Delta$  ADCs are tolerant of component mismatch and circuit non-idealities as compared to Nyquist rate converters. They do not require front-end sample-and-hold circuits, but just an antialias filter with a relaxed frequency-response characteristic.

Single loop  $\Sigma\Delta$  modulators are quite tolerant of finite op-amp DC gain, especially for the op-amps after the first stage. Non-ideal effects are most critical for the first stage op-amps which require less distortion than the others. Noise, offset and harmonics in the second and subsequent op-amps stages are attenuated by the in-band gain of the previous ones. Hence, designing the first op-amps is the most difficult.

Using a fully differential architecture presents numerous advantages: it allows easy implemention of negative coefficients; attenuates the supply and substrate noise; partially cancels out the effects of clock feedthrough and charge injection from switches; and reduces the even-order harmonic distortion.

## 4.1 Fully Differential SC Resonator

#### 4.1.1 Existing SC BP $\Sigma\Delta$ modulator circuits

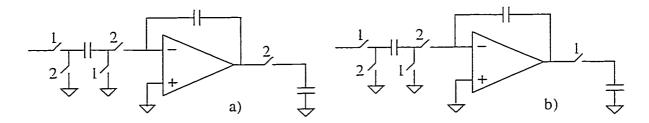

Different bandpass sigma-delta modulators have been reported, and some of them will be presented in this section. The approach in [Singor94] uses the op-amps in the configuration of Figure 4.1 to design LDI (Lossless Discrete Integrator) and FE (Forward Euler) modulators. The circuit of Figure 4.1.b) settles faster than the one of Figure 4.1.a) because, on both phases of the clock, the op-amp drives only two capacitors (sampling and integrating on phase 2, integrating and loading on phase 1 whereas all three capacitors are connected on phase 2 for the circuit of figure a).

Figure 4.1 Op-amps of LDI and FE structures of [Singor94].

The circuit of Figure 2.8 was used in [Longo93]. Using just one more capacitor than the above circuits realises a full delay. The settling time is comparable to the circuit of Figure 4.1.b.

The circuit of Figure 4.2 is a single sampling SC resonator that uses a four-phase non-overlapping clock to be able to realize two delays using just a single op-amp [Hairapetian 96]. On phase 1 the sampling capacitors charges from the input signal. The

Figure 4.2 Pseudo-two-path resonator.

holding capacitors  $C_H$ , that were previously charged at the input voltage one clock earlier minus the output voltage two clocks before, transfer their charge to one of the pair capacitors  $C_A$  or  $C_B$ , (depending on which of phases A1 or B1 is high). Next, on phase 2 the sampling capacitors transfer their charge (stored on previous phase 1 from the input voltage) to the holding capacitors. Simultaneously, one of  $C_A$  or  $C_B$ , (again depending on which of phases B1 or A1 is high) that previously (3/2 clocks earlier) stored the output voltage charge, transfer their charge (with negative sign: notice the inverted connection) to  $C_H$ . For more clarity, lets consider just the case of only one capacitor pair: on phase A1

the capacitors  $C_A$  store the output from  $C_H$ , on B2 and B1 they float, and on A2 they transfer their charge to the output that subtracts from the charge due to the sampling capacitors discharge to  $C_H$ . In this way a two-clock delay is realized for the output voltage (across  $C_A$ ). The capacitors  $C_B$  do the same thing but on later phases (B1  $\rightarrow$  A2  $\rightarrow$  A1  $\rightarrow$  B2). The output voltage is available on phase 1. Writing this out, one can find the relation  $V_{out} = V_{in} \cdot z^{-1} - V_{out} \cdot z^{-2}$  that describes a one-delay resonator.

#### 4.1.2 Four-path Resonator

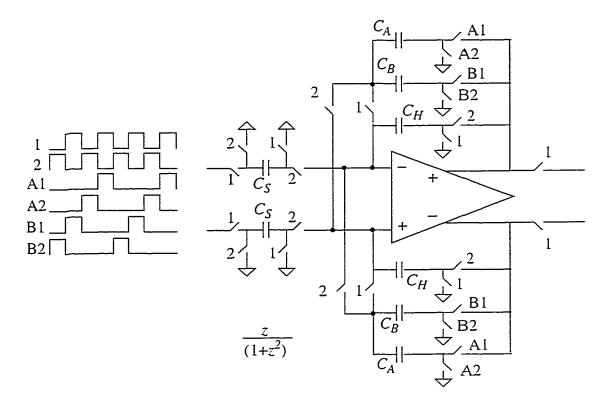

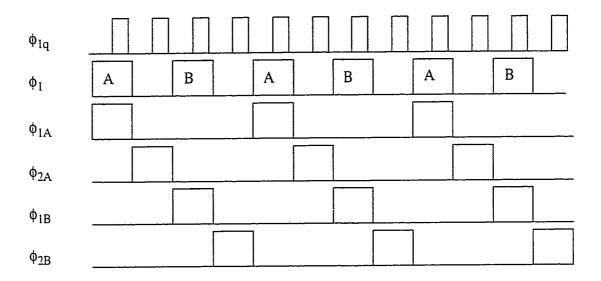

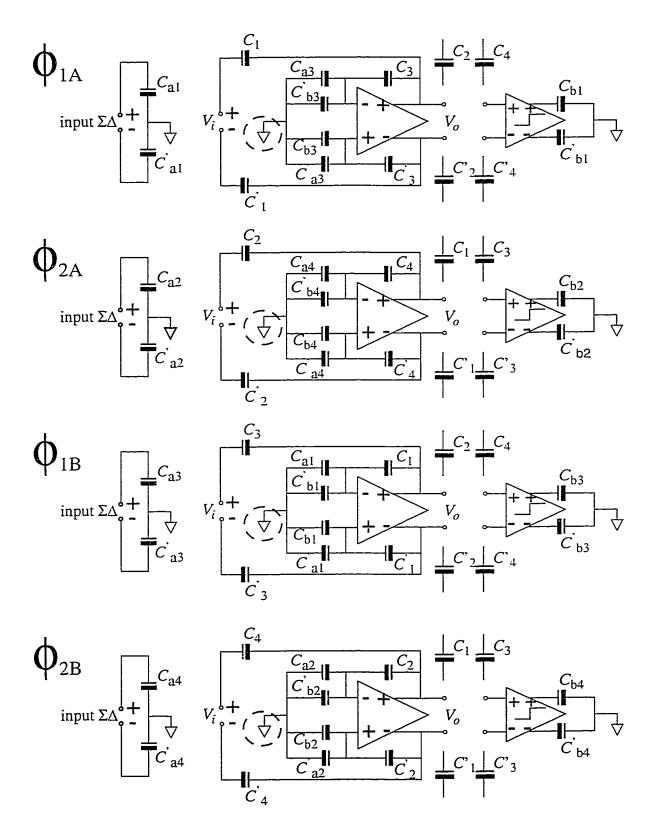

The circuits of section 4.1.1 are single sampled. The one we propose for the sixth-order  $\Sigma\Delta$  modulator is a novel four-path circuit using a four-phase non-overlapping clock. The clock waveforms are shown in Figure 4.3. The resonator and its connections on each phase of the clock  $(\phi_{1A}, \phi_{2A}, \phi_{1B}, \phi_{2B})$  are shown in Figure 4.4; the input of the modulator and the quantizer are also represented to show the way the feedback and forward coefficients are implemented.

The op-amp configuration of Figure 4.4 implements one of the resonators blocks  $A_1$ ,  $A_2$ , or  $A_3 \left( = \frac{1}{1+z^2} \right)$  of Figure 3.4. The resonator's equation is given by EQ 4.1, where  $V_i$  and  $V_o$  are respectively the input and the output differential voltage of the resonator.

$$V_0 \cdot z^2 = V_i - V_0$$

EQ 4.1

Figure 4.3 Clock waveforms for: quantizer  $(\phi_{1q})$ , op-amp CMFB  $(\phi_1)$ , resonator  $(\phi_{1A}, \phi_{2A}, \phi_{1B}, \phi_{2B})$ .

This means that one output sample should be equal to the input minus the output sample two clocks earlier. This is realized by charging a capacitor between the input and the output voltage of the resonator, then keeping it floating for one clock period, after which the capacitor is flipped and connected between the output and the input of the op-amp (the bold plate is solely to show the connection of the capacitor).

To implement the resonator four pairs of capacitors  $C_i$ ,  $C_i$ , are needed, where i=1,2,3,4. On each phase of the clock ( $\phi_{1A}$ ,  $\phi_{2A}$ ,  $\phi_{1B}$ ,  $\phi_{2B}$ ) only two capacitor pairs are connected, while the other two are floating. Of those that are connected, one is between the input and the output of the resonator, and the other one is between the input and the output of the opamp.

For example on  $\phi_{1A}$  the capacitors  $(C_1, C_1')$  are charged to  $(V_i - V_o)$ , on  $\phi_{2A}$  they are floating, and on  $\phi_{1B}$  they are flipped (notice their bold plate as compared to their connection on  $\phi_{1A}$ ) and connected between the input and the output of the op-amp. The capacitors  $(C_2, C_2')$ ,  $(C_3, C_3')$  and  $(C_4, C_4')$  do the same things but on later phases  $(\phi_{2A} \rightarrow \phi_{1B} \rightarrow \phi_{2B})$ ,  $(\phi_{1B} \rightarrow \phi_{2B} \rightarrow \phi_{1A})$  and  $(\phi_{2B} \rightarrow \phi_{1A} \rightarrow \phi_{2A})$ .

For more clarity, this is what happens only on phase  $\phi_{1A}$ : the capacitors  $C_1$  and  $C_1$ ' are charged to  $(V_i - V_o)$ ,  $C_3$  and  $C_3$ ' are flipped and connected between the input and the output of the op-amp, while  $C_2$ ,  $C_2$ ',  $C_4$ ,  $C_4$ ' are floating.

To implement a forward  $(\alpha_1, \alpha_2 \text{ or } \alpha_3)$  or a feedback coefficient  $(\beta_1, \beta_2, \beta_3 \text{ or } \beta)$ , four sets of capacitors  $C_{ai}$ ,  $C_{ai}$ , or  $C_{bi}$ ,  $C_{bi}$  are needed, where i=1,2,3,4. For example, for a forward coefficient, on  $\phi_{1A}$  the capacitors  $C_{a1}$  and  $C_{a1}$  are charging from the differential input voltage of the  $\Sigma\Delta$  modulator,  $C_{a3}$  and  $C_{a3}$  are transferring their charge to  $C_3$  and  $C_3$ , while  $C_{a2}$ ,  $C_{a2}$ ,  $C_{a4}$ ,  $C_{a4}$  are floating. On the next clock phases things are the same if you circularly rotate the indices i=1,2,3,4 of all the capacitors. The implementation for a feedback coefficient is the same as for a forward one with the difference that we don't charge from the input voltage of the  $\Sigma\Delta$  modulator, but from the differential reference voltage of the quantizer's DAC.

To implement a negative coefficient simply invert the differential input. The  $\alpha_1$  forward coefficient can be more easily implemented if the input signal is directly connected to the

Figure 4.4 Four-path two-delay resonator.

first resonator, and not using the sampling capacitors. This saves the eight capacitors corresponding to  $\alpha_1$  implementation. Consequently, all the forward coefficients will be scaled to the values given by EQ 4.2. The signal transfer function is still flat in passband, but its level is shifted from 0 dB to 10 dB. Because of this the maximum signal allowed to the input of the modulator accordingly decreased by 10dB.

$$\alpha_1 = \frac{-0.303053}{0.303053} = -1$$

$$\alpha_2 = \frac{0.18726}{0.303053} = 0.6179117$$

$$\alpha_3 = \frac{-0.501538}{0.303053} = -1.65495$$

EQ 4.2